1.名词解释:

FPGA:现场可编程门阵列,一般工艺SRAM(易失性),所以要外挂配置芯片。

CPLD:复杂可编程逻辑器件,一般工艺Flash(不易失)。

ASIC:专用集成电路

SOC:片上系统

SOPC:片上可编程系统

2.Verilog语法类:

①Verilog两大数据类型:一类是线网类型,另一类是寄存器类型。

线网类型表示硬件电路元件之间实际存在的物理连线,有很多种:wire、tri、wor等等,当然日常使用wire最多,其他的都没遇到过。

寄存器类型表示一个抽象的数据存储单元,只能在initial或always内部被赋值,并且变量的值将从一条赋值语句保持到下一条赋值语句。有5种:reg、time(64位无符号的时间变量)、integer(32位带符号的整数型变量)、real/realtime(64位带符号的实数型变量)。reg用的最多。

②Verilog建模方式:结构化描述方式、数据流描述方式、行为描述方式、混合描述方式。

结构描述是指通过调用逻辑原件,描述它们之间的连接来建立逻辑电路的verilog HDL模型。这里的逻辑元件包括内置逻辑门、自主研发的已有模块、商业IP模块。

数据流描述是指根据信号之间的逻辑关系,采用持续赋值语句描述逻辑电路的方式。通过观察是否使用assign赋值语句可以判断是否有数据流描述。

行为描述是指只注重实现的算法,不关心具体 的硬件实现细节。这与C语言编程非常类似。通 过观察是否使用initial 或always语句块可以 判断是否有行为描述。

混合描述是指以上几种描述方法都存在的一种 描述方式。具体在一个工程中,不可能只是用 单独哪一种描述方式,一般都是各种描述方式 的混合。

3.VHDL相对于Verilog不能描述的层级?

网上有段话说的是:Verilog在其门级描述的底层,即晶体管开关级的描述方面比VHDL更强一些,所以即使使用VHDL的设计环境,在底层实质上也会由Verilog描述的器件库所支持。

Verilog较为适合系统级、算法级、RTL级、门级、开关级的设计,而对于特大型(千万门级以上)的系统设计,则VHDL更为适合。(VHDL比较严谨,而Verilog可以花式编码)

所以,VHDL不能描述开关级。

4.阻塞与非阻塞的区别:

对于代码:

1 //blocking; 2 begin 3 B = A; 4 C = B + 1; 5 end 6 //non-blocking; 7 begin 8 B <= A; 9 C <= B + 1; 10 end

在always语句内部过程赋值语句有两种,阻塞赋值语句与非阻塞赋值语句。

两者主要区别是完成赋值操作的时间不同,阻塞赋值语句的赋值操作是立即执行的,即执行后一句的时候,前一句的赋值已经完成;而非阻塞赋值语句的赋值操作到结束顺序语句块时才完成赋值操作,即赋值操作完成后,语句块的执行也就结束了。即阻塞是串行执行,非阻塞是并行执行的。对于上述代码,阻塞赋值中相当于C = A + 1;非阻塞赋值中B先前的值被A替代,但C的值是B先前值加1。

5.亚稳态是什么怎么解决亚稳态?

另一篇文章已经阐述。

6.竞争冒险是什么,怎么解决竞争冒险?

另一篇文章已经阐述。

7.状态机。

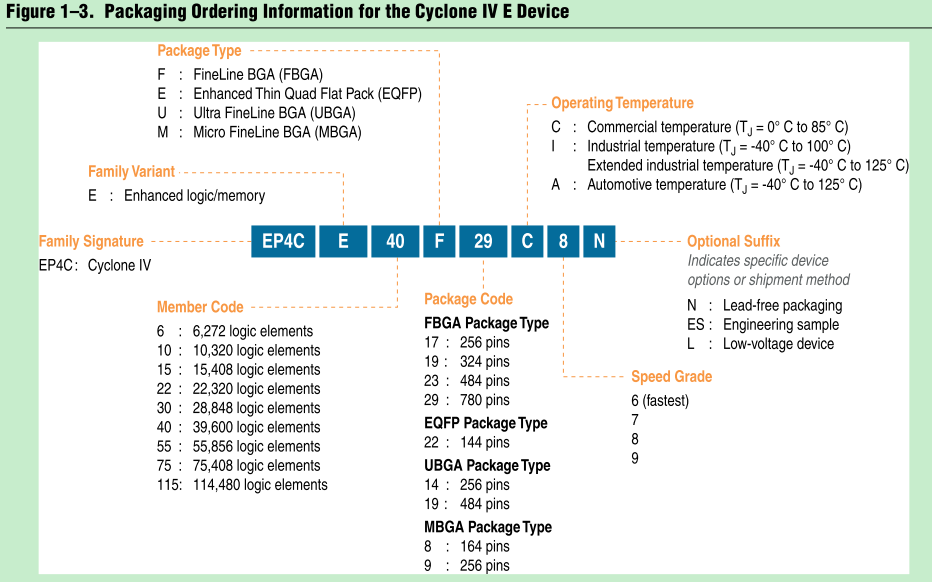

8.你使用的器件名称含义?

以上。