前面说到:

1、nios软核程序标配CFI flash 和Sdram(sdram),flash 存储程序(也可以XIP),sdram运行程序。

2、对于板子上没有falsh和sdram的,可以把程序存在EPCS falsh(配置flash)里,上电运行在on_chip ram(rom)里。

感谢以下链接:http://www.cnblogs.com/liu_xf/archive/2011/10/23/2221880.html

方法1、将NIOS的软件sys_lib中.text等软件文件配置成on-chip-ram,然后生成on-chip-ram.hex,用来初始化sopc中reset-vector中的on-chip-flash的on-chip-ram,.hex作为ram初始化文件,编译后生成.sof和.pof,AS进FPGA后,断电重启后,程序从epcs中复制到on-chip-ram中运行。

ram的大小目前设置为2048.00Kbtes,约200Kbytes,nios的流水灯程序大小为17+182Kbytes,windows下显示为485kb。

测试quartus下102400,8位hex文件,windows下显示大小为1500kb。

注意:这里是程序reset-vector在on-chip-ram里,sys-lib程序文件全部生成在这个ram里,上电后,程序作为ram的初始化文件,生成pof文件后复制到ram中运行。

在方法2中:

1、sopc的reset-vector配置在epcs-flash里,异常向量在on-chip-ram里,syslib还是配置生成在on-chip-ram里。

2、ram的初始文件还是设置为.hex,当然sopc要加一个epcs-flash的控制部件,然后要引出epcs-falsh的data、SDIo、DCLK和flash-nce引脚作为配置后的普通flash来运行nios软件。

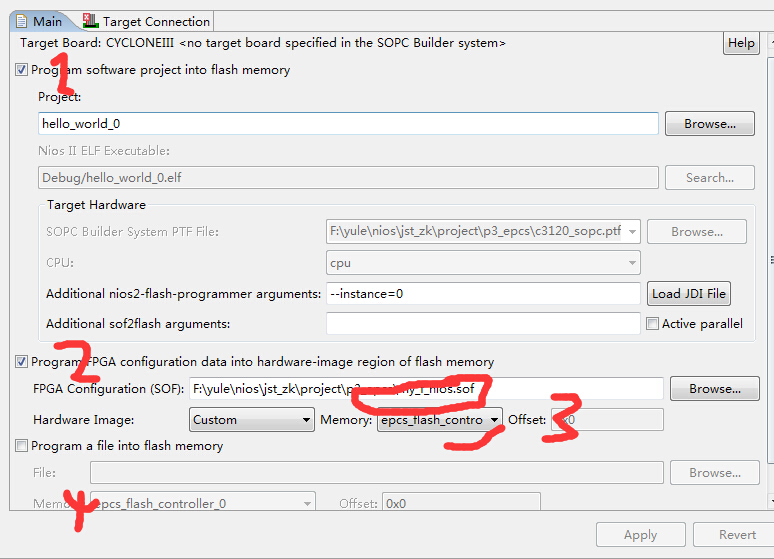

3、quartus下jtag接口把.sof文件配置进fpga,构建基础的flash配置环境;然后用nios的flash的program将elf和sof文件配置进epcs里。

4、上电后,程序从epcs中复制到ram中运行,程序异常后可以重新加载(reset-vector);而不是向方法1,程序是作为.hex文件初始化来运行的,程序异常只能断电重新初始化。(这个是本人猜想的,后期测试)。

---------------------------------------以下是连接的文章,帮我走出困境,感谢------------------------------------

http://www.cnblogs.com/liu_xf/archive/2011/10/23/2221880.html

摘要:

在nios中,有hardware和software,分别有两个文件,如果固化到系统中,需要进行二次下载。下载hardware还好,直接在quartus programer里操作就行,可是software却要在nios ii IDE里操作,不是很方便。再说了,nios ii download elf的时候经常会出一些问题,不知道是软件bug的原因还是什么,本人在nios ii 10.0下对ep3c16下载elf总是不成功,于是采用了一个新的方法,总算将hw和sw固化成功了。

介绍:

软件版本:10.0

硬件:EP3C16240 M25P64

在nios ii 下用flash programer时,弹出如下提示:

#!/bin/sh

#

# This file was automatically generated by the Nios II IDE Flash Programmer.

#

# It will be overwritten when the flash programmer options change.

#

cd D:/vga_board_hdl_code/hello_nios_cy3/software/hello_world_0/Debug

# Creating .flash file for the FPGA configuration

"$SOPC_KIT_NIOS2/bin/sof2flash" --epcs --input="D:/vga_board_hdl_code/hello_nios

_cy3/hello_cy3.sof" --output="hello_cy3.flash"

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert --device=EPCS128 --option=hello

_cy3.opt D:/vga_board_hdl_code/hello_nios_cy3/hello_cy3.sof hello_cy3.pof

Info: Quartus II Convert_programming_file was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 93 megabytes

Info: Processing ended: Sun Oct 23 17:21:45 2011

Info: Elapsed time: 00:00:02

Info: Total CPU time (on all processors): 00:00:02

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert hello_cy3.pof hello_cy3.rpd

Info: Quartus II Convert_programming_file was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 91 megabytes

Info: Processing ended: Sun Oct 23 17:21:50 2011

Info: Elapsed time: 00:00:04

Info: Total CPU time (on all processors): 00:00:04

# Programming flash with the FPGA configuration

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x00000000 --sidp=0x0

0001818 --id=1579616574 --timestamp=1319355357 --instance=0 "hello_cy3.flash"

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Reading System ID at address 0x00001818: verified

: Checksumming existing contents

00000000 : Verifying existing contents

00010000 : Verifying existing contents

00020000 : Verifying existing contents

00030000 : Verifying existing contents

00000000 : Reading existing contents

00010000 : Reading existing contents

00020000 : Reading existing contents

00030000 : Reading existing contents

Checksummed/read 61kB in 12.9s

00000000 ( 0%): Erasing

Erase failed at offset 0

Leaving target processor paused

# Creating .flash file for the project

"$SOPC_KIT_NIOS2/bin/elf2flash" --epcs --after="hello_cy3.flash" --input="hello_

world_0.elf" --output="epcs_flash_controller.flash"

# Programming flash with the project

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x00000000 --sidp=0x0

0001818 --id=1579616574 --timestamp=1319355357 --instance=0 "epcs_flash_controll

er.flash"

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Reading System ID at address 0x00001818: verified

: Checksumming existing contents

00030000 : Verifying existing contents

00030000 : Reading existing contents

Checksummed/read 42kB in 4.4s

00030000 ( 0%): Erasing

Erased 64kB in 0.0s

00030000 ( 0%): Programming

Program failed

Leaving target processor paused

有时又没有failed的信息

#!/bin/sh

#

# This file was automatically generated by the Nios II IDE Flash Programmer.

#

# It will be overwritten when the flash programmer options change.

#

cd D:/MySoftwares/QuartusII/Mywork/sopc_project/led_test/software/led_test/Debug

# Creating .flash file for the FPGA configuration

"$SOPC_KIT_NIOS2/bin/sof2flash" --epcs --input="D:/MySoftwares/QuartusII/Mywork/

sopc_project/led_test/led_test.sof" --output="led_test.flash"

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert --device=EPCS128 --option=led_t

est.opt D:/MySoftwares/QuartusII/Mywork/sopc_project/led_test/led_test.sof led_t

est.pof

Info: Quartus II Convert_programming_file was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 70 megabytes

Info: Processing ended: Wed Mar 30 12:34:48 2011

Info: Elapsed time: 00:00:02

Info: Total CPU time (on all processors): 00:00:02

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert led_test.pof led_test.rpd

Info: Quartus II Convert_programming_file was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 68 megabytes

Info: Processing ended: Wed Mar 30 12:34:51 2011

Info: Elapsed time: 00:00:03

Info: Total CPU time (on all processors): 00:00:02

# Programming flash with the FPGA configuration

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x01001800 --sidp=0x0

1002018 --id=1794073991 --timestamp=1301451768 --instance=0 "led_test.flash"

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Reading System ID at address 0x01002018: verified

: Checksumming existing contents

00000000 : Verifying existing contents

00010000 : Verifying existing contents

00020000 : Verifying existing contents

00000000 : Reading existing contents

00010000 : Reading existing contents

00020000 : Reading existing contents

Checksummed/read 54kB in 1.4s

00000000 ( 0%): Erasing

00010000 (33%): Erasing

00020000 (66%): Erasing

Erased 192kB in 1.9s (101.0kB/s)

00000000 ( 0%): Programming

00010000 (33%): Programming

00020000 (66%): Programming

Programmed 139KB +53KB in 3.3s (58.1KB/s)

Did not attempt to verify device contents

Leaving target processor paused

# Creating .flash file for the project

"$SOPC_KIT_NIOS2/bin/elf2flash" --epcs --after="led_test.flash" --input="led_tes

t.elf" --output="epcs_controller.flash"

# Programming flash with the project

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x01001800 --sidp=0x0

1002018 --id=1794073991 --timestamp=1301451768 --instance=0 "epcs_controller.fla

sh"

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Resetting and pausing target processor: OK

Reading System ID at address 0x01002018: verified

: Checksumming existing contents

00020000 : Verifying existing contents

00020000 : Reading existing contents

Checksummed/read 42kB in 1.1s

00020000 ( 0%): Erasing

Erased 64kB in 0.6s (106.6kB/s)

00020000 ( 0%): Programming

Programmed 23KB +41KB in 0.7s (91.4KB/s)

Did not attempt to verify device contents

Leaving target processor paused

但重启电源后,NIOS不运行,甚至连config_done的灯都常亮(hw配制完成后,应该是灭的),看来连前面固化的pof都给冲掉了。

在cyclone和cyclone ii上都是可以的,从来没出过这种问题,现在cyclone iii上却总是不成功,Altera说是9.0软件的bug,在9.0 SP2上面解决了,可我又没有SP2,换成10.0后还是不行;开始怀疑是不是硬件问题,但我用JTAG和AS模式都可以,而且用JTAG 下载JIC也正常,FLASH换成EPCS4也是一样,这说明硬件是没问题的,可能问题在epcs_contoller和nios ii里面。

苦寻数日,终未解决,后以只好另寻它法。

心想,即然JTAG下载JIC到FLASH正常,那么能不能将HW和HS合并成一个JIC呢,答案是肯定的。

1、将HW和SW合成一个JIC文件

需要的文件:sof,elf;

step1:先将硬件映像和软件映像转换成flash文件

打开nios II command shell,输入:

sof2flash --input=hello_cy3.sof --output=hwimage.flash --epcs --verbose

elf2flash --input=hello_world_0.elf --output=swimage.flash --epcs --after=hwimage.flash --verbose

step2: 把flash文件转化成hex文件

nios2-elf-objcopy -I srec -O ihex hwimage.flash hwimage.hex

nios2-elf-objcopy -I srec -O ihex swimage.flash swimage.hex

step3:打开Quartus® II Convert Programming File 工具,给Flash Loader添加器件类型,然后添加第2步转化出来的hex文件。添加hex文件时,选中“绝对地址”选项。

点击Gererate,即生成了jic文件,再检查生成的 .map 文件有hwimage.hex在起始地址0x0,swimage.hex文件在hwimage.hex结束地址后的起始地址1

hwsw_file.map显示了地址信息

BLOCK START ADDRESS END ADDRESS

hwimage.hex 0x00000000 0x00030FA5

swimage.hex 0x00030FA6 0x0003131D

Note: All the addresses in this file are byte addresses

当然了,也可以只转换swimage,hwimage直接用sof就可以了,不过,这个我没试,这里有说明

http://www.altera.com.cn/support/kdb/solutions/rd10132010_126.html

最后,下载JIC文件,哈哈,NIOS综于跑起来了。

2、将HW和SW合成一个SOF文件

其实在quartus中,也能像Xilinx 的EDK那样将hw和sw合成同一个bitstream。但是SW必须是在片内运行的。

我们知道,NIOS II是不需要自已写bootloader的,NIOS II帮你写好了,但是只能从指定的FLASH Loader,但如果你要从其它的存储器Loader,比如说SD卡,那么就要自已写bootloader了,这样可以将bootloader和sof合成一个文件。

这个方法,无需在SOPC Builder内添加epcs_controller模块;

将CPU的reset地址和vector设置在onchip_mem;

generate之后,无需立即重新编译Quartus 工程。

在Nios II IDE中将system library的的program memary(.text)等,都设为onchip_mem;如下图:

再重新build project。

这个时候Nios II IDE自动创建onchip_memory初始化文件onchip_memory.hex,保存在与SOPC Builder系统文件(.ptf)同一个文件夹下。

然后重新编译Quartus 工程,则自动将onchip_memory.hex内容包含在sof和pof文件中。

然后在 Quartus Programmer中用AS模式下载POF就可以了。再重新上电,发现NIOS 就跑起来了。

结语:

NIOS 出问题后不是很好解决,有些问题很难通过console输出的信息来判定问题所在,再加上编译的时间较长,这也增加了测试的时间。当然咯,有些是软件bug,但也有些是时序问题,比如说你对sopc builder里面做修改后,综合出来的结果会不一样,warring也不一样,例如,我在quartus 10.0里nios在onchip_memory能跑到100M,SDRAM 140M,但改成在sdram里运行后,RUN时,提示verifly错误,NIOS不能运行。改成90M 100M就可以了。所以说,掌握对warring的理解,和新的解决方法也是很不错的,必竟时间是有限的,只要目的达到了,就OK了,你说呢。

-----------------------------end--------------------------------------

1、nios的学习告一段落,上述的轻型nios配置一下试验,搞些简单的外设可以,用的很少,nios高级核还要收费,altera这个很坑跌,限制了nios的使用。

2、nios的学习和使用主要是为了C5中的arm A9双核做准备,这个总是免费使用的吧;跟xilinx的zynq-7000是一样的,直接形成竞争。

3、将来FPGA和arm必将合并到一个芯片中;也如Intel预测,嵌入式芯片和x86电脑的酷睿核一样,最终合并走到一起,不再区分嵌入式和计算机芯片了;此处立言为证。

4、当然,目前的arm+fpga还是以成本、可靠占据未来很长的市场。