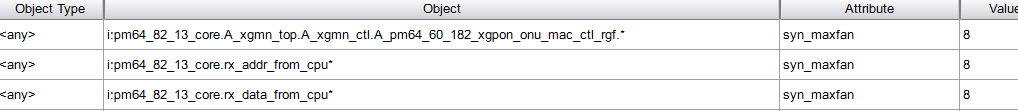

时序约束中synplify的约束也是重要,在fdc表格中可以设置syn_maxfan,syn_maxdelay,syn_preserve,这样避免了修改代码!

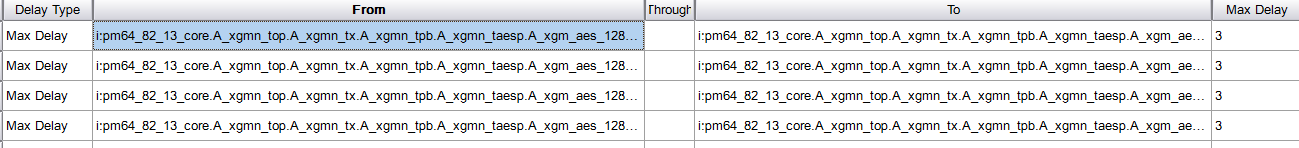

max_delay的好处是限定了综合结果的级数

1)synplifyPro 菜单 Run/Constraint check

Inapplicable constraints 可以检查是否有没有加上的约束

如下显示表示没有问题

#### SUMMARY ############################################################

Found 0 issues in 0 out of 22 constraints

##### DETAILS ############################################################

Inapplicable constraints

************************

(none)

************************

define_attribute { i:pm64_82_13_core.rx_addr_from_cpu* } { syn_maxfan } { 8 }

@E:"d:/new_xgpon/prj/synthesis/synthesis_shannon.fdc":34:0:34:0|Object 'pm64_82_13_core.rx_addr_from_cpu_1c_4[0]' is a keepbuf. Constraint on keepbuf object is not allowed.

@E:"d:/new_xgpon/prj/synthesis/synthesis_shannon.fdc":34:0:34:0|Object 'pm64_82_13_core.rx_addr_from_cpu_1c_4[1]' is a keepbuf. Constraint on keepbuf object is not allowed.

2)菜单Analysis/Timing Analyst 可以看到指定路径的logic level

会生成.ta 文件和.sm(图形显示路径。看到级数)