FPGA图像处理之行缓存(linebuffer)的设计一

作者:OpenS_Lee

1 背景知识

在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。

2 FPGA实现

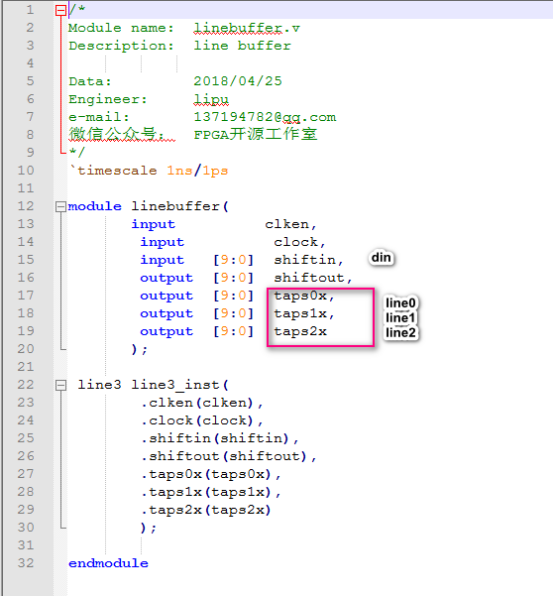

图1 行缓存菊花链结构

如图1所示,我们要设计n行同时输出,就串联n行。Line_buffer的大小设置由图像显示行的大小(图像宽度)决定。例如480*272 (480)。

2.1 设计一Intel shift register

设计源码:

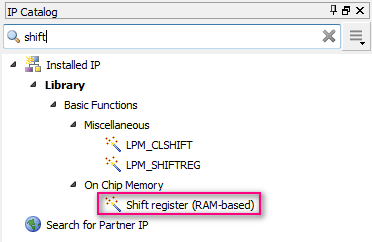

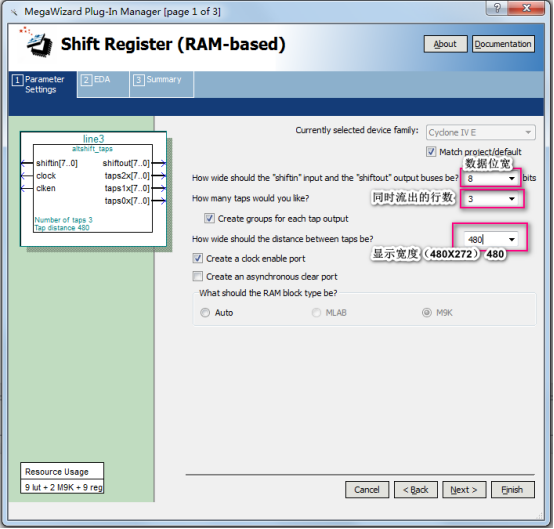

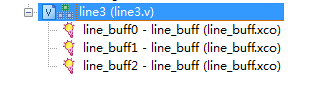

Line3 IP设置:

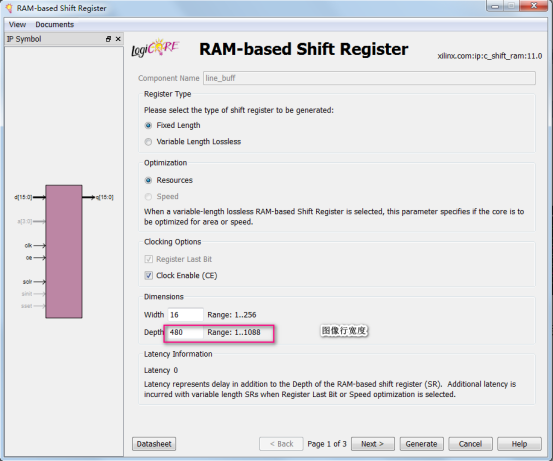

图2 shift register IP

图3 参数设置

如图2,3所示,我们需要设计3x3的矩阵数据,就要同时流出三行的数据参数如图3所示设置。

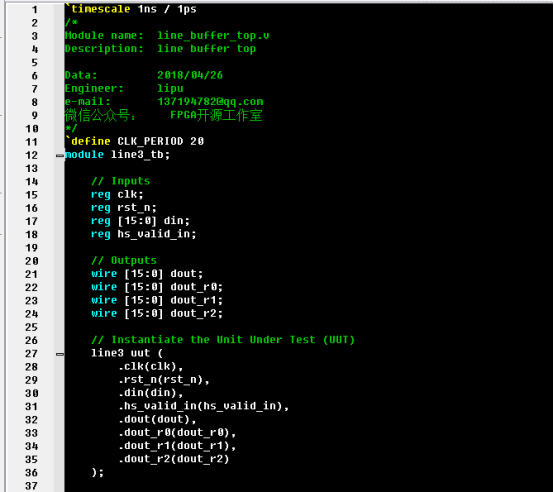

仿真顶层:

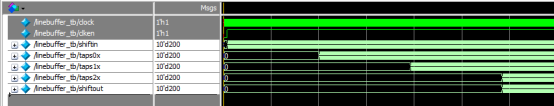

仿真结果:

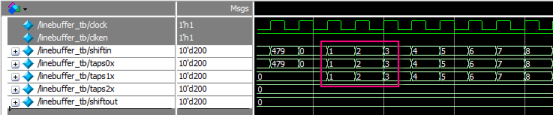

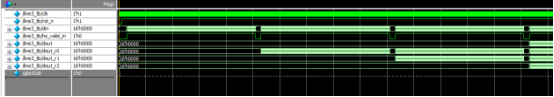

图4 整体效果

图5 一行数据

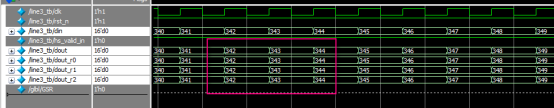

图6 两行数据

图7 三行数据

如图7所示,当三行数据全出来时,我们数据全部对齐,说明设计正确。

2.2 设计二xilinx shift register

源码:

IP设置:

图8 IP设置参数

图9 Hierarchy

仿真顶层:

仿真结果:

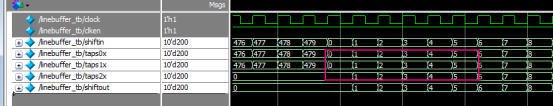

图10 仿真整体效果

图11 三行数据同时对齐输出

至此我们完成了xilinx 和altera 的IP设计行缓存,但是此方法在某种情况下不够灵活,所以下节我们将推出fifo设计行缓存。

欢迎关注微信公众号:FPGA开源工作室