时钟架构总览

7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求。Clock Management Tiles(CMT)提供了时钟合成(Clock frequency synthesis),倾斜矫正(deskew),过滤抖动(jitter filtering)功能。非时钟资源,例如本地布线,不建议使用在时钟设计中。

- 全局时钟树(Global clock tree)可以驱动device中的所有同步原件(synchronous elements)

- IO和区域时钟树(Regional clock tree)可以驱动最多三个垂直连接的时钟区域

- 每一个CMT包括了一个MMCM(Mixed-mode clock manager)和一个PLL(Phase-Locked Loop)。两者存在于的CMT柱(CMT Column)中,而CMT柱则在IO柱(IO Column)旁边。

为了满足不同的时钟使用需求,每一个7系的device都把时钟分成了区域(Regions)

- 根据不同的device大小,时钟区域从最少的4个到最大的24个

- 一个时钟区域包括了所有的同步元件(例如: CLB, IO, Serial Transceivers,DSP, Block RAM, CMT),也包括了50个CLBs和一个IO bank,在时钟区域的中间还有一个水平的时钟Row(HROW,Horizontal clock ROW)

- 每一个时钟区域在HROW的上下各有25个CLB

垂直时钟线和水平时钟线将时钟分成了很多区域。

每列时钟域包含50个CLB,10个36kb的block RAMs,20个DSP slices和12个BUFHS(水平时钟缓冲器)。

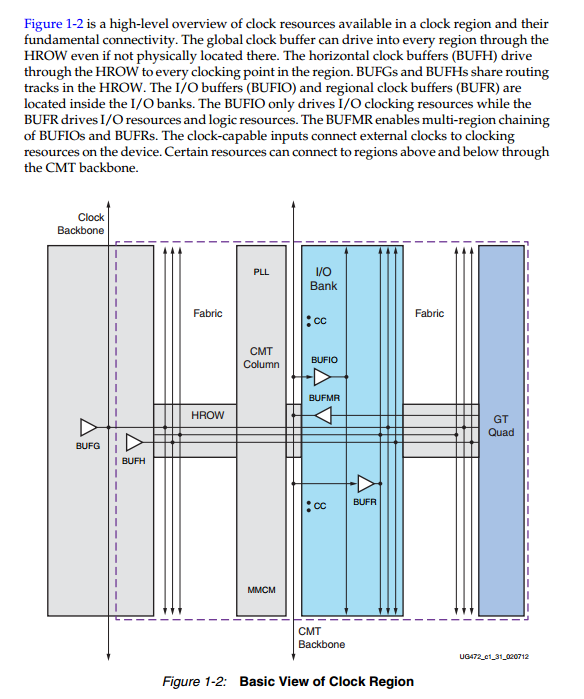

上图为一个时钟域基本的连接结构,

全局时钟缓冲器(BUFG)能够通过HROW(水平时钟行)驱动所有区域,

水平时钟缓冲(BUFH)驱动器通过HROW到该区域的每一个时钟点。

在HROW中,BUFG和BUFH共享路径。

BUFIO和BUFR都在IO bank里面,BUFIO只驱动IO资源,BUFR驱动IO资源和逻辑资源。

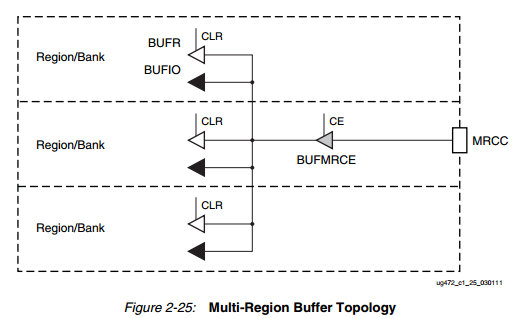

BUFMR支持多区域链接BUFIOs和BUFRs。

时钟输入与外部时钟相连,确定的资源能够连接到CMT的骨架上。

MRCC/SRCC是区域时钟的BUFIO,MRCC能驱动相同、上下相邻bank/时钟区域的IO,SRCC只能驱动相同bank/时钟区域的IO。

GCLK是全局时钟网络的BUFIO。

CCLK是配置时钟IO。

全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

区域时钟资源是独立于全局时钟网络的。Xilinx的器件分成若干个时钟区域,以Virtex-6为例,Virtex-6的最小器件有6个区域,最大器件有18个区域。它与全局时钟不同,区域时钟信号X只能驱动限定的时钟区域。

HROW(时钟行):

全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

区域时钟资源是独立于全局时钟网络的。Xilinx的器件分成若干个时钟区域,以Virtex-6为例,Virtex-6的最小器件有6个区域,最大器件有18个区域。它与全局时钟不同,区域时钟信号X只能驱动限定的时钟区域。

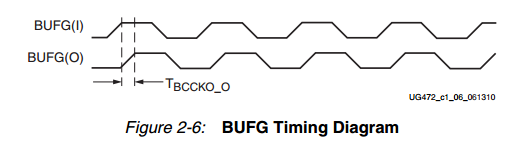

BUFG(全局时钟网络时钟驱动器):

时钟信号要走全局时钟网络,必须通过这个BUFG来驱动,BUFG可以驱动所有的CLB,RAM,IOB。spartan6 有一共有16个BUFG全局时钟线。virtex-6则一共有32个BUFG全局时钟线。

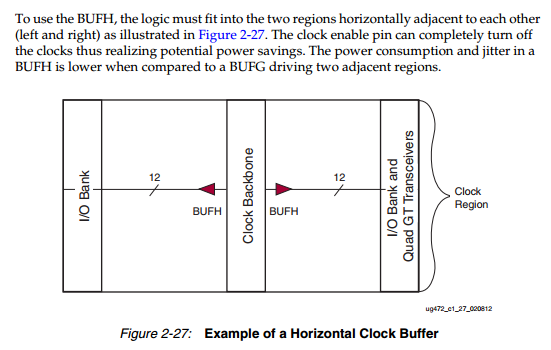

BUFH(水平全局时钟树):

BUFH驱动区域中的水平全局时钟树,Xilinx的时钟是通过时钟树来分布的。

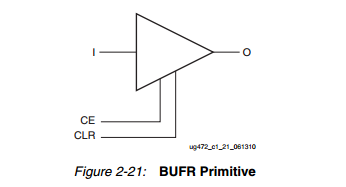

BUFR(区域时钟缓冲器):

要进入区域时钟网络,必须例化BUFR。一个BUFR最多可以驱动三个相邻的时钟区域中的区域时钟。顶部和底部区域中BUFR只能连接相邻的一个时钟区域,也就是说,顶部的BUFR连接它所在的下面一个相邻区域。底部的BUFR只能连接它所在的上边一个相邻区域。因此,底部和顶部BUFR的作用区域为两个时钟区域。

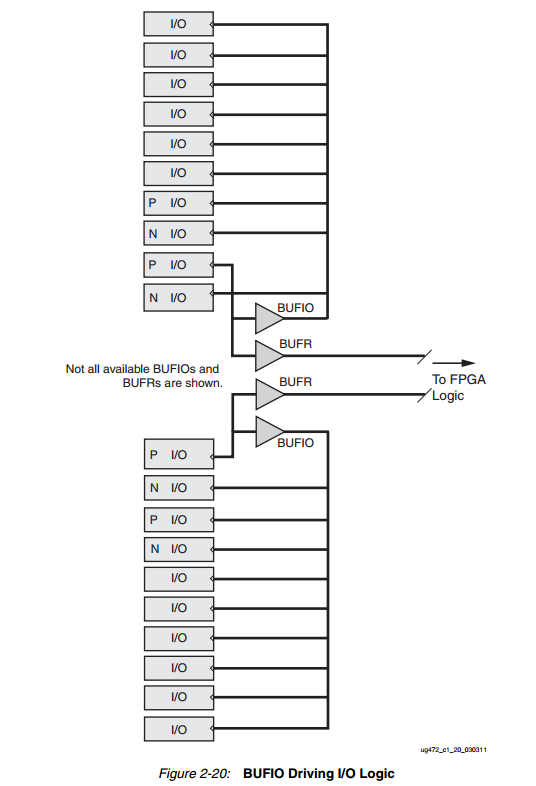

BUFIO:

UFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BUFIO,其中的2个可以驱动相邻区域的I/O时钟网络。BUFIO不能驱动逻辑资源(CLB、BRAM等),因为I/O时钟网络只存在于I/O列中。

时钟布线总览

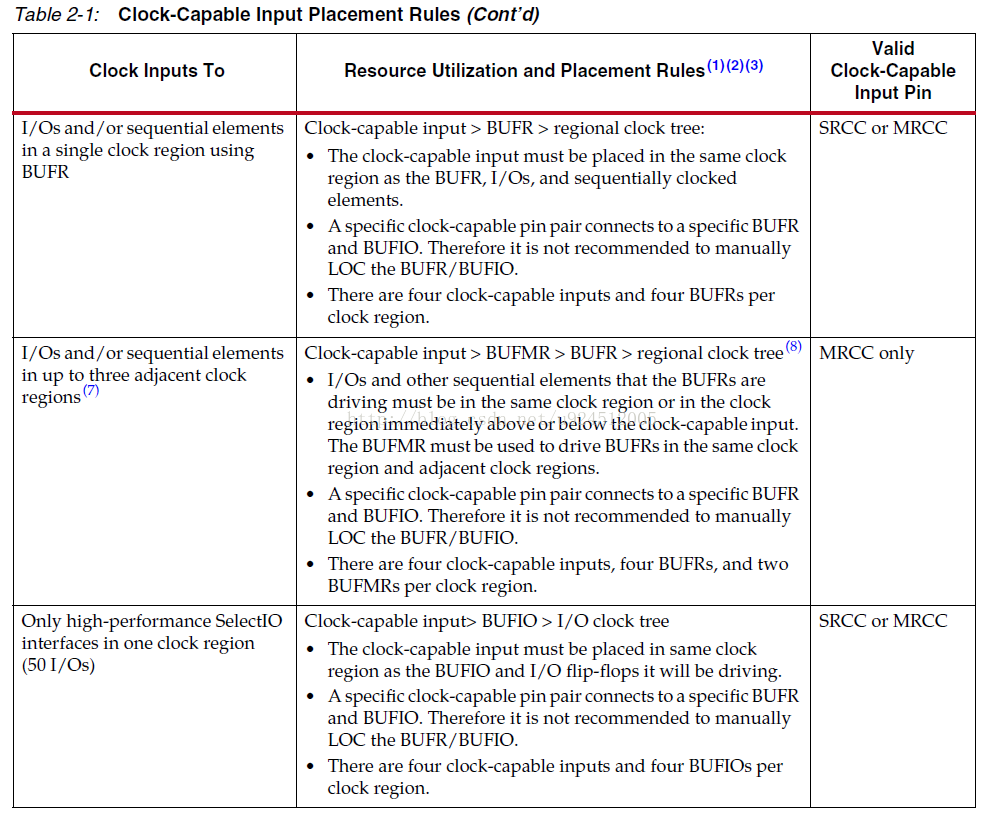

每一个IO bank都含有clock-capable input pin来帮助外部时钟进入到7系的FPGA时钟资源里。在专属clock buffer的帮助下,clock-capable input带来时钟:

- 全局时钟分布于device的上下两部分

- IO时钟分布于与之相同的IO bank和垂直相邻的IO bank中

- 区域时钟分布于与之相同的时钟区域中和垂直的相邻时钟区域

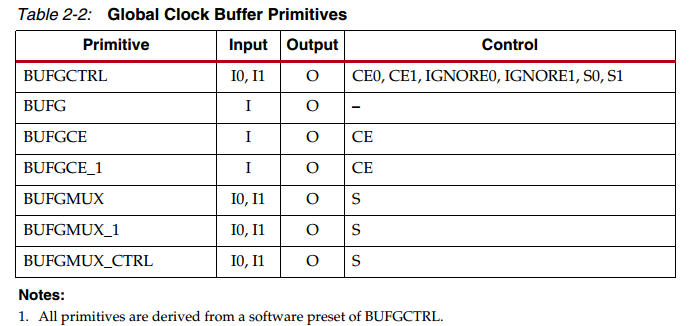

7系的device有32个全局时钟线,可以提供时钟和控制信号到所有的时序资源中。全局时钟buffer(BFUG)用来驱动全局时钟线且必须用于驱动全局时钟线。每一个时钟区域可以支持最多12个这样的全局时钟,12条全局时钟使用水平时钟线(HROW)来进入时钟区域

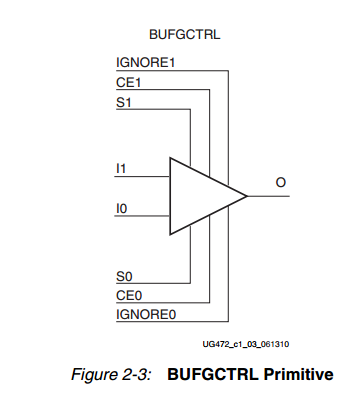

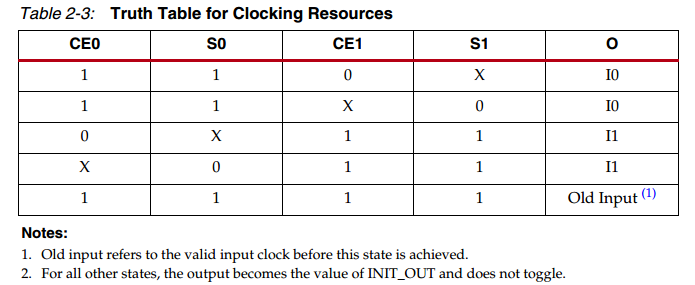

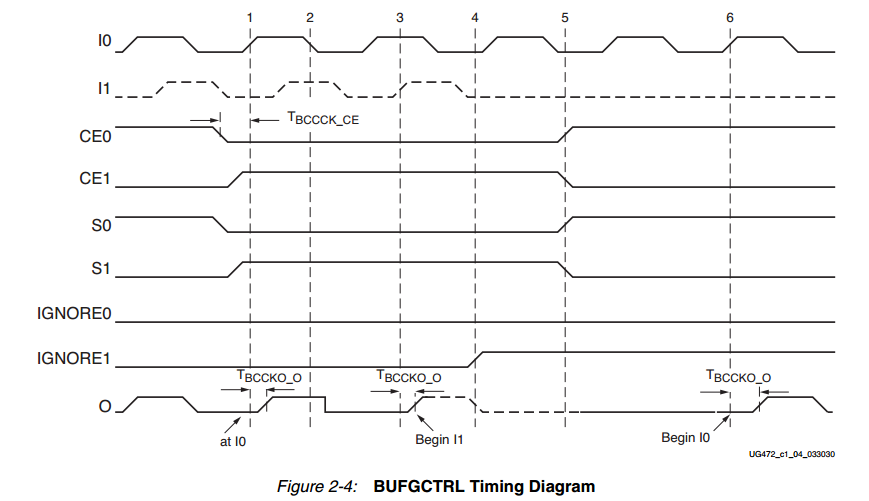

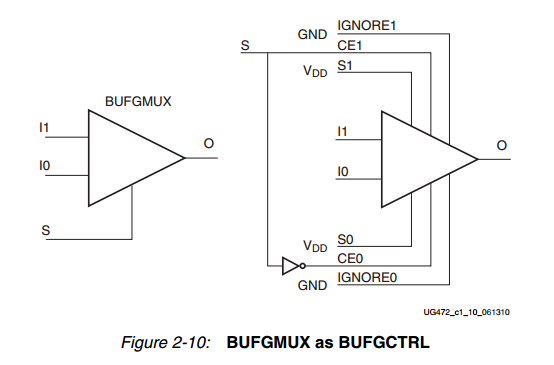

对于全局时钟buffer(BUFG)来说:

- 对于跨越多个时钟区域的时钟,此buffer可以用于clock enable或disable

- 作为一个glitch-free multiplexer

- 在两个时钟源做出选择

- 从一个废弃的时钟中退出

- 经常被CMT驱动

- 消除clock distribution delay

- 根据另外的clock调整clock delay

水平的时钟buffer(BUFH)允许使用HROW访问全局时钟线。它也可以作为一个clock enable电路(BUFHCE)来独立的enable或者disable。每一个时钟区域使用12条水平时钟线来支持最多12个时钟。

每一个7系FPGA有区域和IO时钟树来驱动同时钟区域的所有的时序资源。每个device也有多时钟区域buffer(BUFMR)来允许IO和区域时钟能垂直跨越三个时钟区域。

- IO时钟buffer(BUFIO)驱动IO时钟树,访问同一个IO bank中的所有时序IO资源

- 区域时钟buffer(BUFR)驱动区域时钟树(regional clock tree)来驱动同一个时钟区域中的所有时钟资源且可以用于分频(divide)时钟频率

- 在IOB中的serializer/deserializer的帮助下,BUFIO和BUFR时钟buffer允许源同步的系统(Source-synchronous system)跨越时钟域(clock domain)且不使用额外的逻辑资源

- 相邻的区域和IO时钟树可以使用multi-clock region buffer(BUFMR)来驱动(使用相关的BUFR或者BUFIO时)

- 最多4个唯一(unique)的IO时钟和4个唯一的区域时钟可以被一个时钟区域或者IO bank所支持

CMT到IO的连接使用了高性能时钟布线,每一条布线都是低抖动,最小duty-cycle扭曲的path(minimal duty-cycle distorted direct path)

BUFR经过分频后的时序图:

the span of a regional clock signal (BUFR) is limited to one clock region, one I/O clock signal drives a single bank

The BUFIO drives a dedicated clock net within the I/O bank, independent of the global clocking resources. Thus, BUFIOs are ideally suited for source-synchronous data capture (forwarded/receiver clock distribution).

BUFRs drive clock signals to a dedicated clock net within a clock region, independent from the global clock tree. Each BUFR can drive the four regional clock nets in the region it is located. Unlike BUFIOs, BUFRs can drive the I/O logic and logic resources (CLB, block RAM, etc.). Clock division in the BUFR is controlled in software through the BUFR_DIVIDE attribute.

BUFRs are ideal for source-synchronous applications requiring clock domain crossing or serial-to-parallel conversion. Unlike BUFIOs, BUFRs are capable of clocking logic resources in the FPGAs other than the IOBs. Figure 2-23 is a BUFR design example.

CMT总览

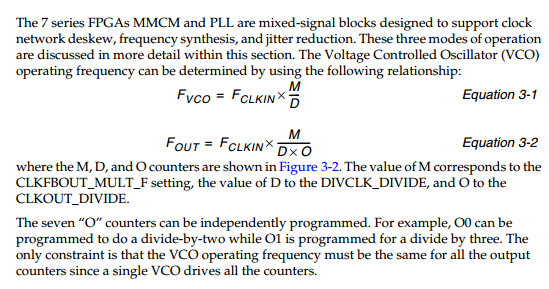

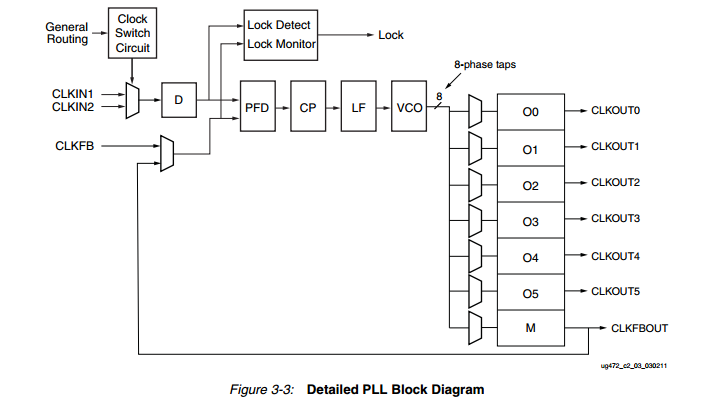

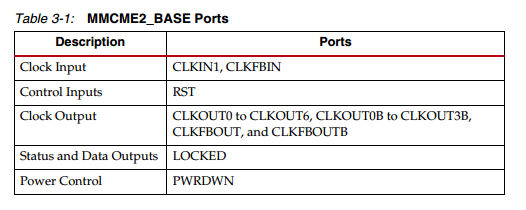

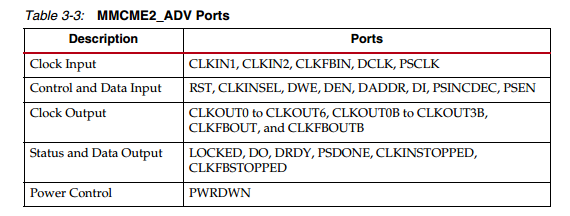

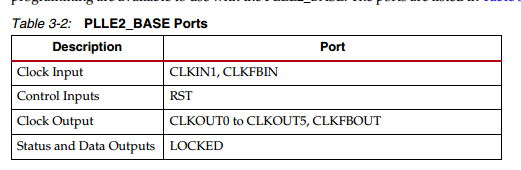

每个7系FPGA有最多24个CMT,每一个由一个MMCM和一个PLL组成。MMCM和PLL提供广范围的频率综合,外部或内部时钟的防抖过滤器(jitter filter)和提供抗扭曲时钟(deskew clock)。PLL包含了一部分MMCM的功能。7系的FPGA时钟输入允许多个资源来提供reference clock到MMCM和PLL

7系的FPGA MMCM有无限的phase-shift能力且可以用于动态phase-shifting模式。MMCM在feedback或者一个output path中也有分数计数器(Fractional counter)功能来提供更好的频率合成能力。

LogiCORE IP可以合理利用MMCM和PLL来创造时钟网(clock network).GUI的画面提供了各种时钟参数。IP可以选择合适的CMT资源和的配置CMT资源和布线资源。

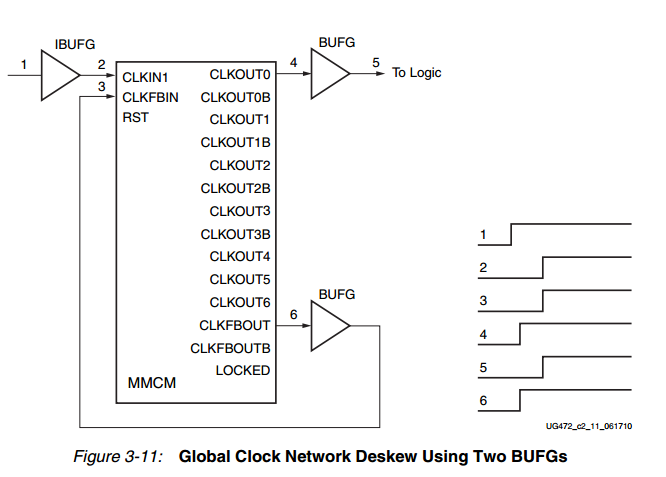

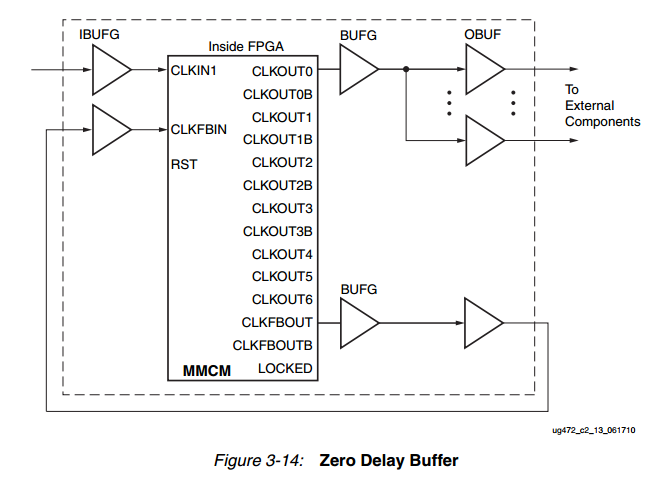

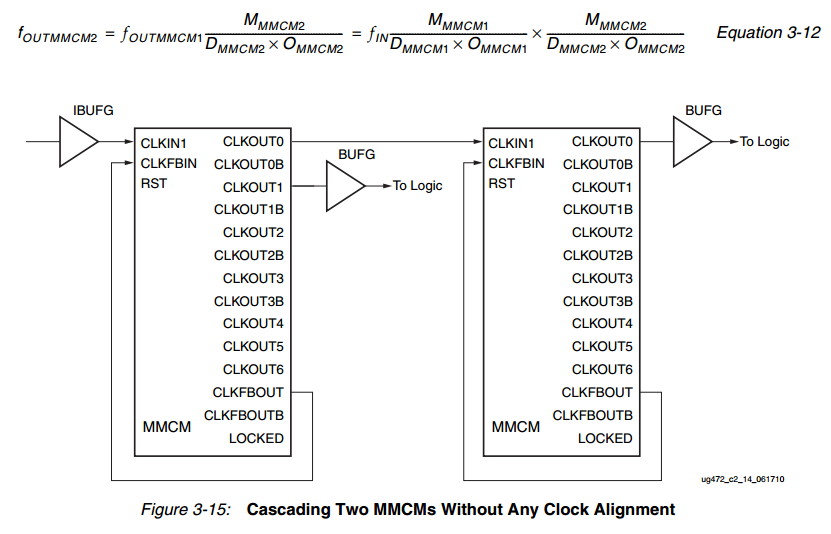

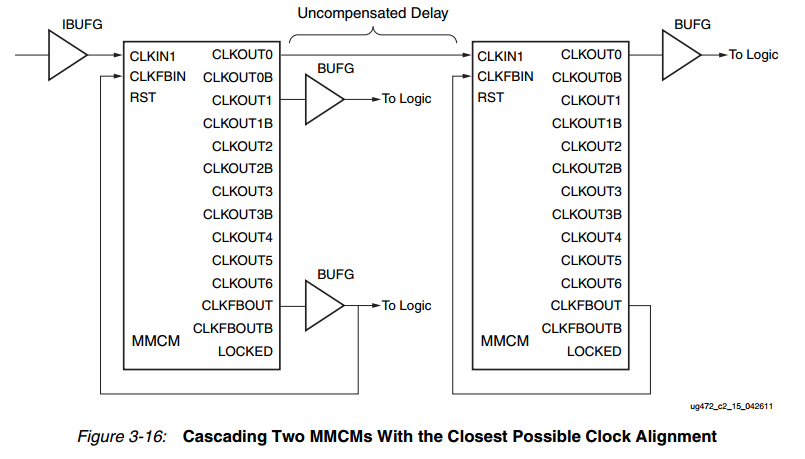

Clock Network Deskew

In many cases, designers do not want to incur the delay on a clock network in their I/O timing budget therefore they use a MMCM/PLL to compensate for the clock network delay. 7 series FPGAs support this feature. A clock output matching the reference clock CLKIN frequency (always CLKFBOUT) is connected to a BUFG in the same half of the device and fed back to the CLKFBIN feedback pin of the MMCM/PLL. The remaining outputs can still be used to divide the clock down for additionally synthesized frequencies.In this case, all output clocks have a defined phase relationship to the input reference clock. The CLKOUT0–CLKOUT3 of either the MMCM or PLL can be used to cascade to other MMCMs/PLLs. However, there is a phase offset on the output clocks between cascaded MMCMs/PLLs.

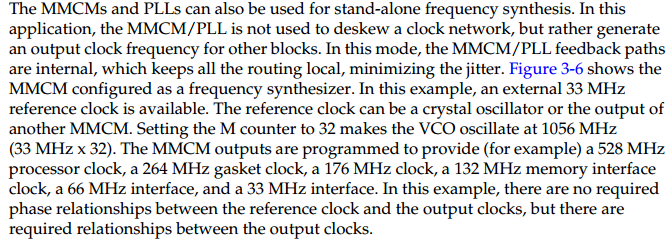

Frequency Synthesis Only Using Integer Divide

将MMCM和PLL当滤波器使用,取出时钟抖动。

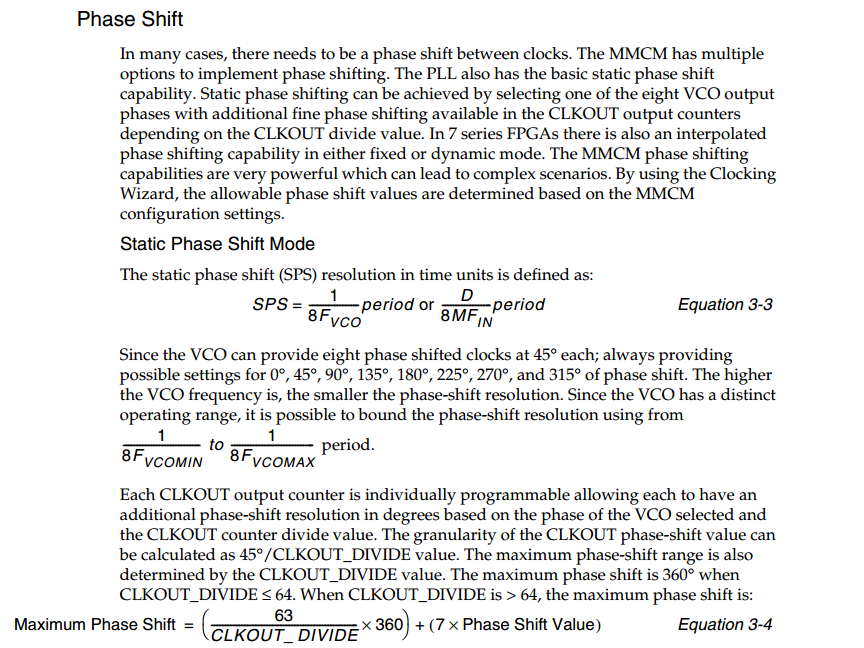

静态相移和动态相移:

1) 静态相移模式。

VCO能够以45°的间隔提供8个移相时钟,静态相移模式通过选择这8个VCO输出相移中的一个实现的。因此以时间为单位的相移分辨率定义为:PS=1/8FVCO或D/8MFIN。因为VCO具有明确的工作范围,所以可以把相移分辨率的范围界定为从1/8 FVCO_MIN到1/8 FVCO_MAX。VCO的频率越高,相移分辨率就越高。各输出计数器可分别编程,允许每个计数器在VCO的输出频率的基础上具有不同的相移。

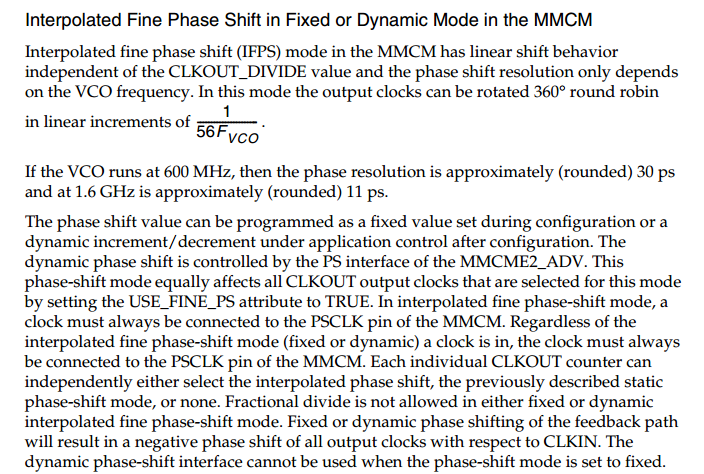

(2) IFPS模式。

Virtex-6还提供一种IPFS模式相移,支持固定或动态模式。在该模式下,相移实现线性移位特性,和CLKOUT_DIVIDE值无关,只决定于VCO频率。MMCM以Fvco/56为步长进行相位调节。相移值可在配置过程中固定,也可动态改变。

CLKOUT计数器可分别设置成静态相移模式或者IPFS模式,固定相移模式下,动态相移接口不能被使用。

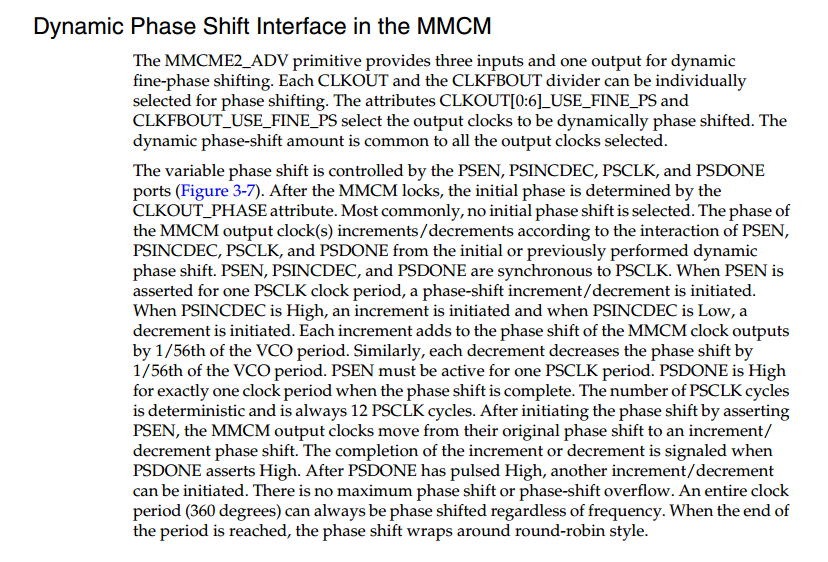

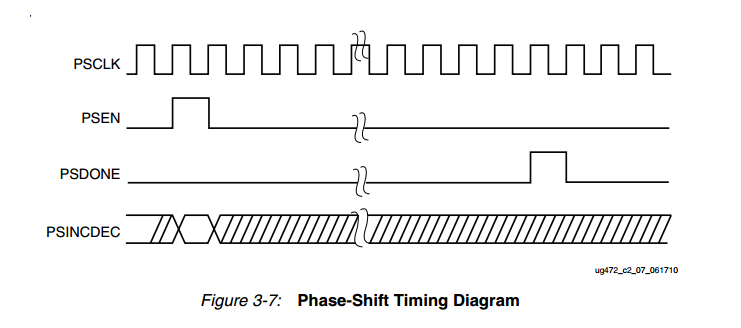

(3) 动态相移接口。

Virtex-6可以由PSEN、PSINCDEC、PSCLK和PSDONE控制动态相移。MMCM锁住后,CLKOUT_PHASE属性决定初始相位,通常情况下,可以不设置初始相移。MMCM根据PSEN、PSINCDEC、PSCLK和PSDONE信号的动作,改变输出相移。步长为VCO时钟周期的1/56。